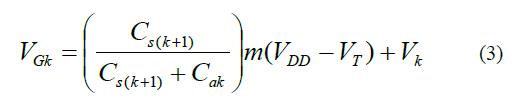

Where m is the number of stages of the gate pump circuit. Cs(k+1) is the capacitance of the (k+1)th gate pump circuit, Cak is capacitance above the gate capacitance of main pump circuit. Since the gate voltage level of the switch transistor (VGk) in main pump circuit turns in the more positive direction, the voltage between the gate and the source of each switch transistor (VGsk) has a larger value than the conventional magnitude, and the voltage drop of the switch transistor is decreased due to a decrease in the RON of the switch transistor resulting from an

increase of the VGS of each switch transistor. Therefore, the small value of RON for the proposed charge pump reduces the conduction power loss in comparison with a Dickson charge pump structure, which is characterized by an increase of the VGS of the switch transistor. Figure 3 shows the timing diagram of the non overlap-ping clock signal.

Contact: Sammy

Skype:

Tel:

Email: sammyfu@electricmotorscn.com

Add: 5th Floor, Building 3, Huafeng Zhenbao Industrial Park ,Beihuan Road, Shiyan Street, Bao'an District, Shenzhen City, China.